Navigating High-Speed USB 3.0 Integration in USB Type-C

In the realm of digital connectivity, USB Type-C has become a key player, particularly for its role in facilitating high-speed USB 3.0 and 3.1 data transfers. This article offers a technical examination of the complex process of multiplexing these high-speed data lines within the reversible USB Type-C architecture. We focus on the nuances of signal management, emphasizing the critical function of multiplexers, such as the TUSB1142, in achieving efficient and reliable connectivity in modern USB-C applications.

Managing USB 2.0 Lines in the USB-C Connector

The USB-C connector's reversibility is a hallmark of its design, offering significant convenience for users. However, this feature introduces complexity in the management of data lines, particularly for USB 2.0 and the high-speed USB 3.0 and 3.1 standards. For USB 2.0, the connector houses duplicated sets of data pins, Dp1/Dn1 and Dp2/Dn2. Unlike high-speed data lines, these USB 2.0 lines do not specifically require an active mux for proper routing.

A simple yet effective solution for managing these USB 2.0 lines on the PCB is to interconnect the Dp and Dn lines underneath the connector and then route a single differential pair to the System on Chip (SoC). This approach allows for the USB 2.0 functionality to be maintained regardless of the cable's orientation, as the data lines are effectively bridged on the PCB. While this method can work adequately, it is not without its trade-offs.

One potential downside of this solution is that it may not be optimal in terms of signal integrity, especially at the higher end of the USB 2.0 speed spectrum. To counteract any signal degradation or loss, the incorporation of a USB 2.0 redriver IC can be considered. The redriver IC helps in restoring the signal quality, ensuring that data transmission remains robust even after bridging the Dp and Dn lines. This becomes particularly important in scenarios where the USB 2.0 lines must travel longer distances on the PCB or when the design constraints impose limitations on the signal path.

In summary, while interconnecting the Dp and Dn lines under the USB-C connector offers a straightforward solution for managing USB 2.0 data in the context of the connector's reversible design, it is crucial for designers to consider the implications on signal integrity. The strategic use of redriver ICs can enhance the performance and reliability of these connections, ensuring that the USB 2.0 standard continues to function effectively in the new realm of USB-C technology.

Optimizing High-Speed Data Routing in USB-C with Multiplexers and CC Detection

In the sophisticated realm of USB-C design, particularly for USB 3.0 and 3.1 standards, the strategic handling of high-speed TX (transmit) and RX (receive) differential pairs is essential. These pairs, delineated as TX1+/TX1- with RX1+/RX1- and TX2+/TX2- with RX2+/RX2-, are essential for managing data transmission and reception in accordance with the connector's orientation.

The multiplexer (mux) plays a critical role, acting as a dynamic switch. It links the single TX and RX differential pairs from the System on Chip (SoC) to the corresponding TX1/RX1 or TX2/RX2 pairs in the USB-C connector. The connector's insertion orientation dictates this routing, requiring the mux to rapidly switch connections based on the detected orientation. Here, the Channel Configuration (CC) detection IC becomes crucial. This IC is responsible for determining the orientation of the USB-C cable upon insertion and sending a signal to the mux, instructing it to align the SoC's TX and RX lines with the appropriate set of differential pairs (TX1/RX1 or TX2/RX2).

This process, facilitated by the CC detection IC, ensures that the mux selects the correct pair for data transmission and reception. For instance, if the CC detection IC signals that the cable is inserted in one orientation, the mux connects the SoC's TX line to TX1+ and TX1-, and the RX line to RX1+ and RX1-. Conversely, if the cable is inserted in the opposite orientation, the connections shift to TX2+/TX2- and RX2+/RX2-.

This dynamic and responsive routing mechanism is not just a functional necessity but also critical for maintaining the high-speed data's signal integrity. Effective isolation of the differential pairs is essential to prevent crosstalk and signal degradation, particularly vital at the high operational frequencies of USB 3.0 and 3.1. Additionally, the mux, in coordination with the CC detection IC, must execute this switching with precise timing to avoid data transmission errors during the transition period.

For engineers and PCB designers focusing on USB-C applications, a comprehensive understanding of the interaction between the mux and the CC detection IC is crucial. This knowledge guides the selection of appropriate components and the design of PCB layouts that accommodate the rapid switching and isolation required for these high-speed signal paths, ensuring optimal functionality and reliability in USB-C enabled devices.

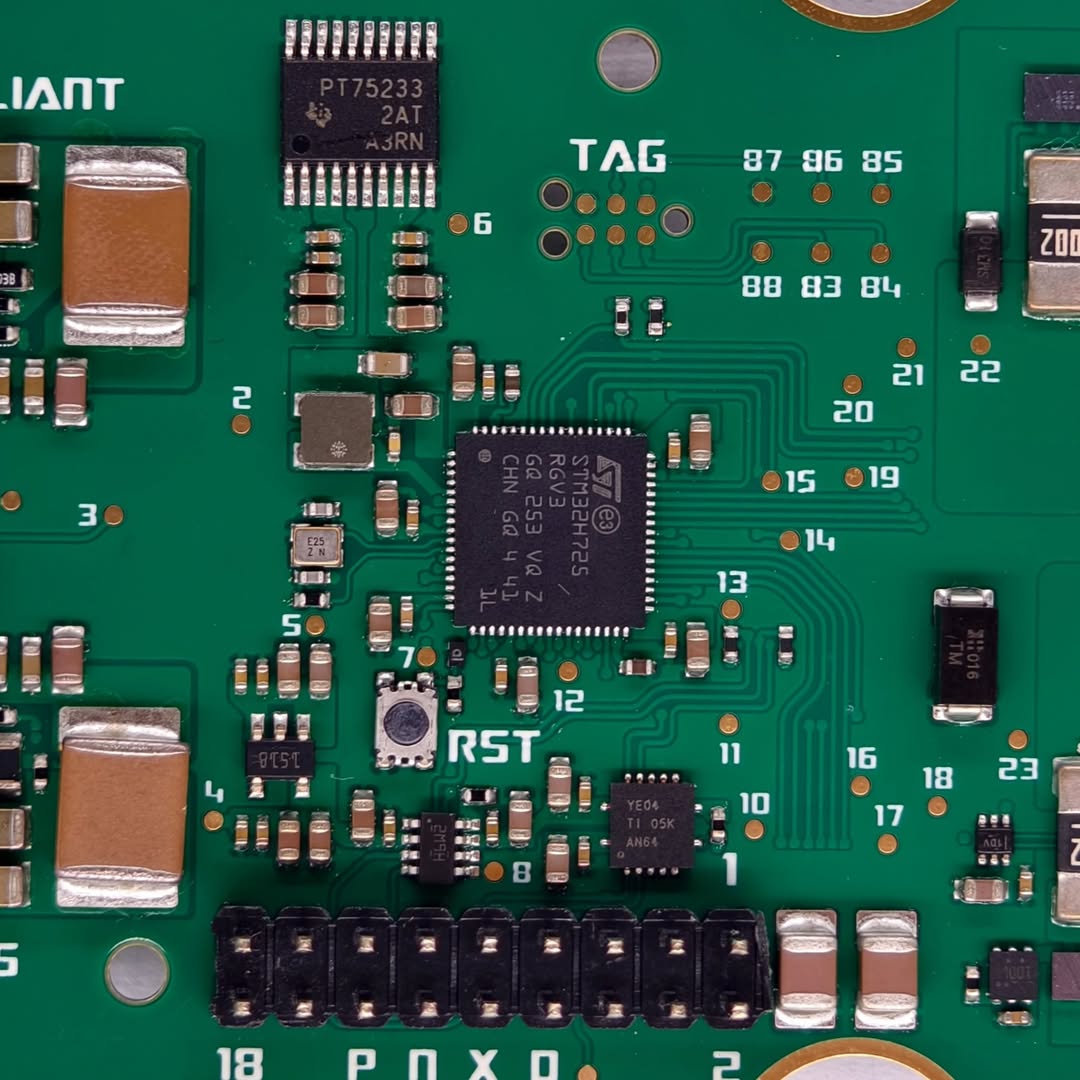

Integration of TUSB1142 in High-Speed USB-C Applications

The TUSB1142, as detailed in its datasheet, is integral for 10 Gbps USB 3.2 operations in USB-C designs, offering proper control over high-speed data lines. Key to its functionality are SSTXn/p and SSRXn/p pins, handling signal inputs, and CTX1n/p, CTX2n/p pins for outputs, aligned with the USB-C's reversible nature. The 'FLIP/SCL' pin, a crucial aspect of this IC, adapts to the connector's orientation, while the I2C interface provides programmable control, enhancing the mux's operational flexibility. This necessitates a meticulous PCB design approach, focusing on minimal signal path lengths, impedance matching, and effective thermal management strategies. Ensuring stable power delivery and robust ESD protection, especially near the USB-C connector, is vital for maintaining the integrity and reliability of high-speed data transmissions.